# JH-7110 Boot User Guide

VisionFive 2

Version: 1.3

Date: 2023/09/07

Doc ID: JH7110-BUGEN-001

# **Legal Statements**

Important legal notice before reading this documentation.

### PROPRIETARY NOTICE

Copyright © Shanghai StarFive Technology Co., Ltd., 2023. All rights reserved.

Information in this document is provided "as is," with all faults. Contents may be periodically updated or revised due to product development. Shanghai StarFive Technology Co., Ltd. (hereinafter "StarFive") reserves the right to make changes without further notice to any products herein.

StarFive expressly disclaims all warranties, representations, and conditions of any kind, whether express or implied, including, but not limited to, the implied warranties or conditions of merchantability, fitness for a particular purpose, and non-infringement.

StarFive does not assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation indirect, incidental, special, exemplary, or consequential damages.

All material appearing in this document is protected by copyright and is the property of StarFive. You may not reproduce the information contained herein, in whole or in part, without the written permission of StarFive.

### **Contact Us**

Address: Room 502, Building 2, No. 61 Shengxia Rd., China (Shanghai) Pilot Free Trade Zone,

Shanghai, 201203, China

Website: http://www.starfivetech.com

Email:

• Sales: sales@starfivetech.com

• Support: support@starfivetech.com

# **Preface**

About this guide and technical support information.

### **About this document**

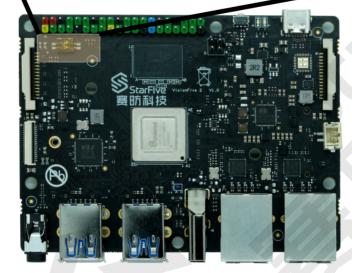

This document mainly provides the StarFive JH-7110 users and partners with a high-level understanding of how their SoC JH-7110 and single board computer VisionFive 2 are boot up.

### **Revision History**

**Table 0-1 Revision History**

| Version | Released   | Revision                                                                                                                                                           |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3     | 2023/09/07 | Updated the boot sequence.                                                                                                                                         |

| 1.2     | 2023/07/14 | Since StarFive no longer recommends JH-7110 users to boot directly from SD card and eMMC, removed all the relevant descriptions and updated the boot flow diagram. |

| 1.1.3   | 2023/05/10 | Updated <u>VisionFive 2 Boot Mode Settings</u> (on page <u>17)</u> .                                                                                               |

| 1.1.2   | 2022/02/02 | Minor change. Corrected a typo in the offset value in Boot Address Allocation (on page 9).                                                                         |

| 1.1.1   | 2022/01/19 | Minor change. Removed duplicate sections delivered also in other documents.                                                                                        |

| 1.1     | 2022/01/18 | Refined the boot process and republish.                                                                                                                            |

| 1.0     | 2022/01/16 | First official release.                                                                                                                                            |

### **Notes and notices**

The following notes and notices might appear in this guide:

. *i*

### Tip:

Suggests how to apply the information in a topic or step.

### Note:

Explains a special case or expands on an important point.

## .

### Important:

Points out critical information concerning a topic or step.

## • CAUTION:

Indicates that an action or step can cause loss of data, security problems, or performance issues.

## • 🚺 Warning:

Indicates that an action or step can result in physical harm or cause damage to hardware.

# **Contents**

| 4. VisionFive 2 Boot Mode Settings | 17  |

|------------------------------------|-----|

| 3. Boot Process Memory Map         | 16  |

| 2. Boot Flow                       |     |

| 1.7. U-Boot                        |     |

| 1.6. OpenSBI                       |     |

| 1.5. SPL                           |     |

| 1.4. BootROM                       | 10  |

| 1.3. Boot Address Allocation       |     |

| 1.2. Boot Sources                  |     |

| 1.1. Overview                      |     |

| 1. Introduction                    |     |

| Preface                            | iii |

| Legal Statements                   | ii  |

| List of Figures                    | 7   |

| List of Tables                     | 6   |

5

# **List of Tables**

| Table 0-1 Revision History                   | ii       |

|----------------------------------------------|----------|

| Table 1-1 Values for Boot Source Selection   | <u>S</u> |

| Table 1-2 16 M Flash Boot Address Allocation | <u>9</u> |

| Table 1-3 SD/eMMC Boot Address Allocation    | 9        |

| Table 1-4 How BootROM loads resources        | 10       |

| Table 4-1 Boot Mode Settings                 | 17       |

# **List of Figures**

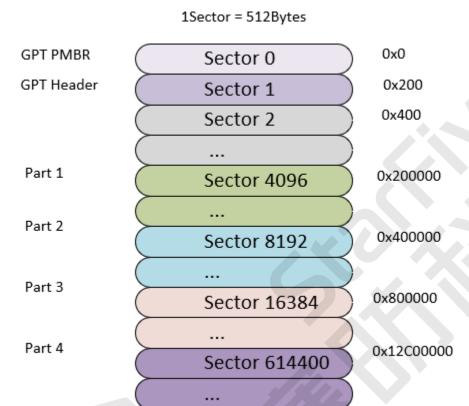

| Figure 1-1 SD/eMMC Boot Address Partitions | 10 |

|--------------------------------------------|----|

| Figure 1-2 OpenSBI Output Example          | 12 |

| Figure 1-3 U-Boot Screen                   | 13 |

| Figure 2-1 Boot Flow                       | 14 |

| Figure 3-1 Boot Process Memory Map         | 16 |

| Figure 4-1 Boot Mode Setting Location      | 18 |

| Figure 4-2 Boot Mode Settings              |    |

# 1. Introduction

## 1.1. Overview

This document is intended to:

- Introduce all the boot stages of booting a Linux operating system on JH-7110.

- Provide instructions for how an image package is generated and where it is located.

- Provide instructions for how to write different media and where to boot.

The code sources referenced in this document are based on the following conditions:

- OpenSBI v1.2

- U-Boot version: 2021.10

- Linux Kernel version: 5.15

- Hardware Board: VisionFive 2 1.2A/1.3B

### Note:

For different U-Boot or Linux Kernel versions, these references may be slightly different.

### **File Locations**

Locate the JH-7110 Software Development Kit (SDK) with the following information.

- Repository: https://github.com/starfive-tech/VisionFive2

- Branch: JH7110 VisionFive2 devel

- Tag: Select the newest tag. For example, VF2 v2.11.5 is newer than VF2 v2.10.10.

## 1.2. Boot Sources

The power domain **AON\_RGPIO** is used to select the boot vector and BootLoader source and offer multiple methods to obtain the BootLoader image.

The JH-7110 SoC can boot from one of the sources listed in the following table, as selected by the AON\_RGPIO[1,0] (0x1702002c).

**Table 1-1 Values for Boot Source Selection**

| Proces-<br>sor | BootROM        | Boot Vector    | Source List                    |

|----------------|----------------|----------------|--------------------------------|

| U74            | 0x00_2A00_0000 | 0x00_1301_0000 | Quad SPI NOR flash memo-<br>ry |

|                |                | 0x00_1000_0000 | UARTO                          |

# 1.3. Boot Address Allocation

The following table shows the boot allocation for 16 M Flash.

Table 1-2 16 M Flash Boot Address Allocation

| Offset   | Length    | Description                    |

|----------|-----------|--------------------------------|

| 0x0      | 0x80000   | SPL                            |

| 0xF0000  | 0x10000   | U-Boot environment variables   |

| 0x100000 | 0x400000  | fw_payload.img(OpenSBI+U-Boot) |

| 0x600000 | 0x1000000 | Reseved                        |

Since document release 1.2, boot from SD Card or eMMC is no longer recommended. But to maintain the code structure, the following SD/eMMC boot address allocations are modified as "reserved". Be aware of this change when designing your device based on JH-7110.

Table 1-3 SD/eMMC Boot Address Allocation

| Offset      | Length      | Description          | Comment             |

|-------------|-------------|----------------------|---------------------|

| 0x0         | 0x200       | GPT PMBR             | 0x4: Backup address |

| 0x200       | 0x200       | GPT Header           |                     |

| 0x400       | 0x1F_FC00   | Reserved             |                     |

| 0x20_0000   | 0x20_0000   | Reserved             | Partition 1         |

| 0x40_0000   | 0x40_0000   | Reserved             | Partition 2         |

| 0x80_0000   | 0x1240_0000 | Initramfs + UEnv.txt | Partition 3         |

| 0x12C0_0000 | End of disk | System rootfs        | Partition 4         |

### 1.4. BootROM

BootROM is a hard-coded boot program written in the address offset of 0x2A00\_0000 on JH-7110. The program is basically used to load and execute the Secondary Program Loader (SPL).

Figure 1-1 SD/eMMC Boot Address Partitions

BootROM enables developers to insert programs from different media accesses, including QSPI flash and UART, by reading SPL to SRAM (0x8000000).

By using the bit of AON\_RGPIO[1,0] (0x1702002c), developers can confirm their boot mode.

The following table explains the procedure of how BootROM loads resources.

Table 1-4 How BootROM loads resources

| RGPIO1 | RGPIO0 | <b>Boot Source</b>             | Comments                                                                                                                                                                                                                    |

|--------|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0    | 0x0    | Quad SPI NOR flash memo-<br>ry | Read SPL from Sector 0.                                                                                                                                                                                                     |

| 0x1    | 0x1    | UARTO                          | When the system detects the boot-mode of UART has been chosen, it will enter Xmodem Receiver Mode. Users can then import recovery programs in Xmodem mode using serial cable connections. Once the files are confirmed with |

Table 1-4 How BootROM loads resources (continued)

| RGPIO1 R | RGPIO0 | <b>Boot Source</b> | Comments                                                                    |  |

|----------|--------|--------------------|-----------------------------------------------------------------------------|--|

|          |        |                    | transmission complete BootROM will run the recovery programs automatically. |  |

### Note:

Besides in the BootROM, you can also change the backup address in the spl\_tool.

## 1.5. SPL

SPL is a boot program based on U-Boot. The primary use of SPL is to facilitate DDR initialization and to load the image file  $fw_payload.img$  (U-Boot + OpenSBI). SPL reads  $fw_payload.img$  from the address 0x100000 and then loads it to the address 0x40000000 of the DDR for operation.

# 1.6. OpenSBI

The binary of OpenSBI is packaged with the binary compiled by U-Boot in the way of payload to generate the final fw\_payload.bin. The main functions of OpenSBI are:

- Provide basic system calls for Linux

- Switch the mode from M mode to S mode

- Jump to 0x4020 0000 (located in DDR) to execute U-Boot

The normal output information is illustrated in the following figure.

### Figure 1-2 OpenSBI Output Example

```

U-Boot SPL 2021.10-00008-g48be500431-dirty (Jun 28 2023 - 18:39:23 +0800)

DDR: 8G version: g8ad50857.

Trying to boot from SPI

OpenSBI v1.2

Platform Name

: StarFive VisionFive V2

Platform Features

: medelea

Platform HART Count

: aclint-mswi

Platform IPI Device

Platform Timer Device

: aclint-mtimer @ 4000000Hz

Platform Console Device : uart8250

Platform HSM Device

Platform PMU Device

Platform Reboot Device

: pm-reset

Platform Shutdown Device : pm-reset

Platform Suspend Device : ---

Firmware Base

: 0x40000000

Firmware Size

: 392 KB

Firmware Size : 392 KB

Firmware RW Offset : 0x40000

Runtime SBI Version

: 1.0

Domain0 Name

: root

Domain0 Boot HART

: 1

Domain0 HARTs

: 0*,1*,2*,3*,4*

: 0x000000002000000-0x000000000200ffff M: (I,R,W) S/U: ()

: 0x0000000040000000-0x000000004003ffff M: (R,X) S/U: ()

: 0x00000000000000000-0xfffffffffffffff M: (R,W,X) S/U: (R,W,X)

Domain0 Next Arg1

: 0x0000000042200000

Domain0 Next Mode

: S-mode

Domain0 SysReset

: yes

Domain0 SysSuspend

: yes

Boot HART ID

Boot HART Domain

: root

Boot HART Priv Version

: v1.11

Boot HART Base ISA

: rv64imafdcbx

Boot HART ISA Extensions : none

Boot HART PMP Count

: 8

Boot HART PMP Granularity : 4096

Boot HART PMP Address Bits: 34

Boot HART MHPM Count

: 0x0000000000000222

Boot HART MIDELEG

```

### 1.7. U-Boot

U-Boot runs at 0x4020\_0000 and works in S mode. It contains basic file system and commonly used peripheral drivers (such as GMAC, UART, QSPI, SDIO, etc.). U-Boot can load the kernel image through ETH (Network), UART, QSPI, SDIO or NVMe (SSD).

### Figure 1-3 U-Boot Screen

```

U-Boot 2021.10 (Nov 10 2022 - 13:29:36 +0800), Build: jenkins-VF2_515_Branch_SDK_Release-12

Model: StarFive VisionFive V2

DRAM: 4 GiB

MMC: sdio0@16010000: 0, sdio1@16020000: 1

Loading Environment from SPIFLash... SF: Detected gd25lq128 with page size 256 Bytes, erase size 4 KiB, total 16 MiB

*** Warning - bad CRC, using default environment

StarFive EEPROM format v2

-----EEPROM INFO-----

Vendor: StarFive Technology Co., Ltd.

Product full SN: VF7110A1-2238-D004E000-000000001

data version: 0x2

PCB revision: 0xal

BOM revision: A

Ethernet MACO address: 6c:cf:39:6c:de:12

Ethernet MAC1 address: 6c:cf:39:7c:ae:13

------EEPROM INFO------

serial@10000000

Out: serial@10000000

serial@10000000

Model: StarFive VisionFive V2

Net: eth0: ethernet@16030000, eth1: ethernet@16040000

switch to partitions #0, OK

mmc1 is current device

found device 1

bootmode flash device 1

Failed to load 'uEnv.txt'

Can't set block device

Hit any key to stop autoboot: 0

StarFive #

```

### Note:

Visit <u>RVspace</u> to make sure you have the most updated files and installation packages from StarFive. Press **Enter** to confirm the operation or for the next command.

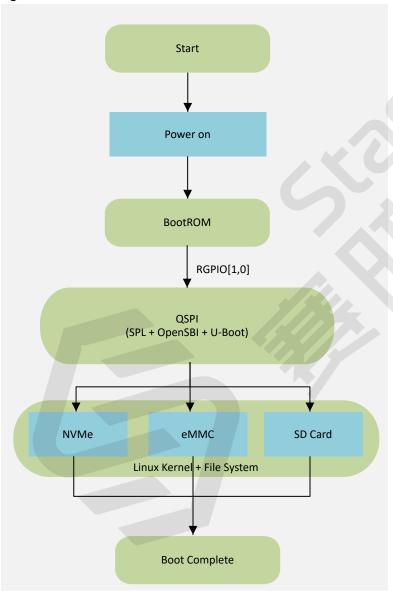

# 2. Boot Flow

This chapter introduces the general boot-up process of the JH-7110 SoC including the image used for boot path, etc.

You can boot from the U-Boot TPL/SPL from StarFive U-Boot, which is the image source code.

The following menu-cascade shows typical JH-7110 boot flow: **BootROM > SPL + Open SBI + U-Boot** > **Kernel + File System > Boot Complete**.

Figure 2-1 Boot Flow

### **Boot Devices**

JH-7110 supports the following boot devices.

QSPI Flash (For SPL + OpenSBI + U-Boot) + SD Card/eMMC /NVMe (For Kernel + File System and later)

### Note:

System will detect in sequence whether it can boot from the following device sequence: **SD > eMMC > NVMe**. For example, if the boot program is found on the SD, eMMC will be ignored.

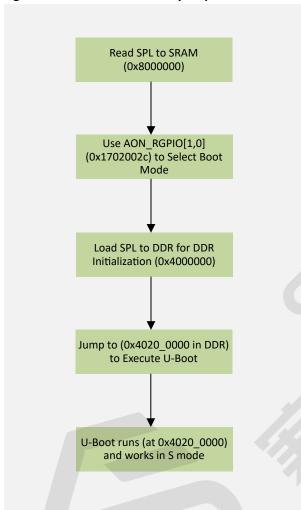

# 3. Boot Process Memory Map

The following diagram shows the memory map of boot process for JH-7110 on VisionFive 2.

Figure 3-1 Boot Process Memory Map

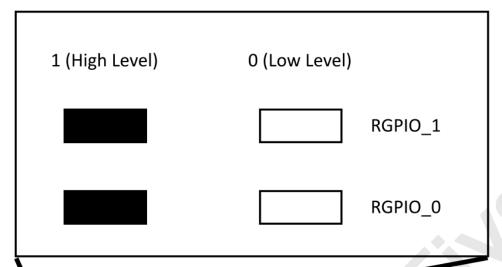

# 4. VisionFive 2 Boot Mode Settings

VisionFive 2 provides pins to determine the boot mode before it is powered up. The following are the available boot modes and details.

**Table 4-1 Boot Mode Settings**

| Index | Boot Mode            | RGPIO_1 | RGPIO_0 |

|-------|----------------------|---------|---------|

| 1     | 1-bit QSPI Nor Flash | 0 (L)   | 0 (L)   |

| 2     | SDIO3.0              | 0 (L)   | 1(H)    |

| 3     | еММС                 | 1 (H)   | 0 (L)   |

| 4     | UART                 | 1 (H)   | 1 (H)   |

StarFive recommends that you use 1-bit QSPI Nor Flash mode since there is a low possibility that the VisionFive 2 may fail to boot in eMMC or SDIO3.0 boot mode. Try restarting the VisionFive 2 if fails to boot in eMMC or SDIO3.0 boot mode.

The following figure displays the location and the pin definitions of the boot mode settings.

Figure 4-1 Boot Mode Setting Location

**Figure 4-2 Boot Mode Settings**

# **QSPI**

RGPIO\_1: 0 (L) RGPIO\_0: 0 (L)

# **SDIO**

RGPIO\_1: 0 (L) RGPIO\_0: 1 (H)

## eMMC

RGPIO\_1: 1 (H) RGPIO\_0: 0 (L)

# **UART**

RGPIO\_1: 1 (H) RGPIO\_0: 1 (H)

Note: H for high level; L for low level.

### Note:

The silk prints may vary with different versions of boards.