Overview

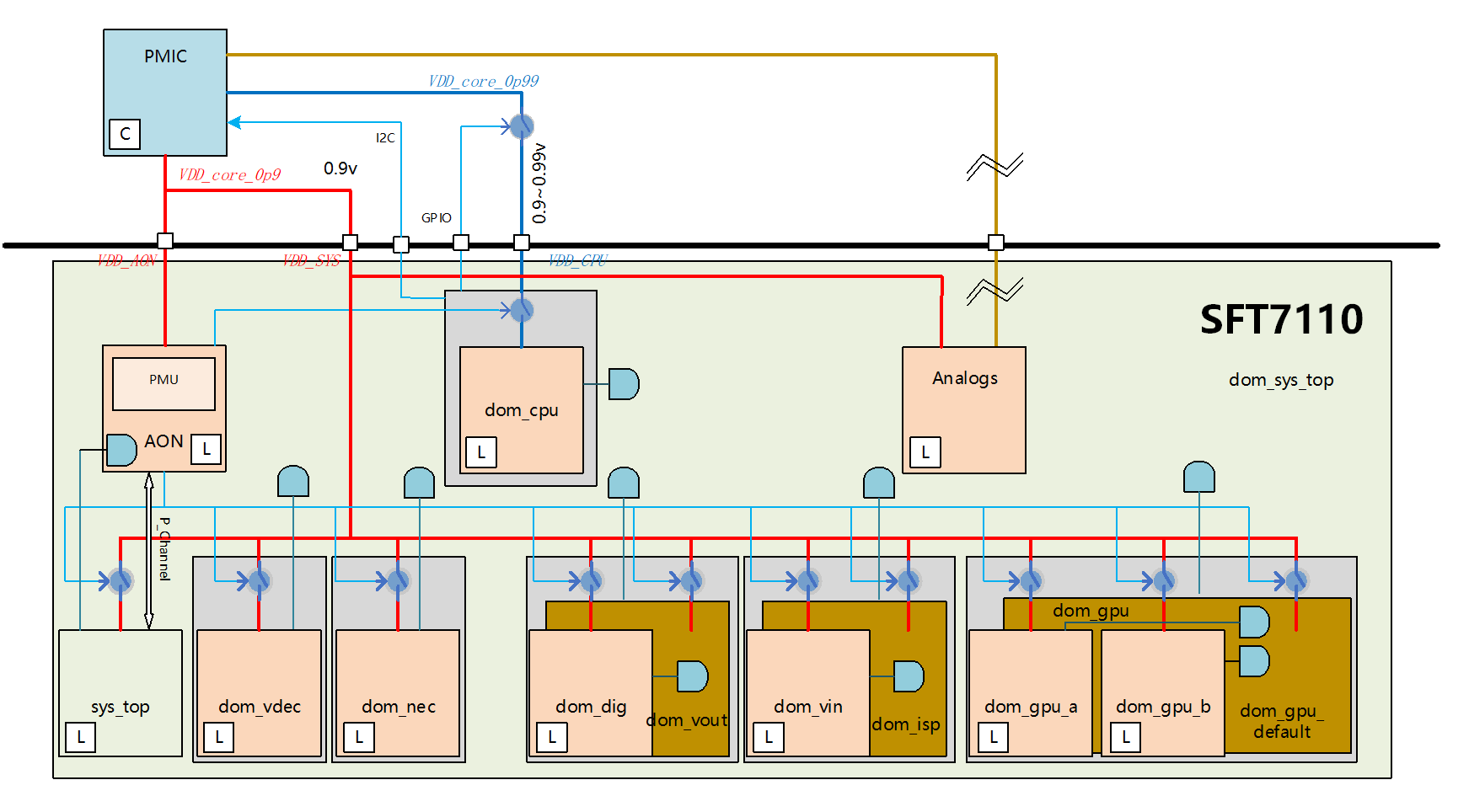

The system includes 10 hierarchies with the prefix of “dom”. Each hierarchy represents an independent power domain. All analog PHY are positioned on the top layer.

In the 10 power domains, dom_aon is a “always-on” power domain. It is used for waking up from sleep. The supported modules include:

- Real Time Clock (RTC)

- General Purpose Input and Output (GPIO)

- Wake-on-LAN (WoL)

The GPU of JH-7110 contains the following 3 power domains.

- dom_gpu_default: Share the same control with the top layer.

- dom_gpu_a: Share the same control with the top layer.

- dom_gpu_b: An independent power domain which enables software power-on and power-off.

LP Cell Placement Architecture

The following list provides the architecture details:

- Overview

- Feeds power from external PMIC

- Includes 3 power groups: Vdd_core_0v9, Vdd_core_0v99, and Vdd_ana

- Vdd_core_0v99 can be switched off on board level

- Power domain

- Includes 8 power domains

- Always-On (AON) domains are the always on modules for the entire SoC.

- The dom_cpu module is for Vdd_core_0p99, and all the other modules are for Vdd_core_0p9;

- The dom_isp, dom_vout, and dom_gpu modules contain 2-3 power domains each, while the other modules only contain 1.

- Power switch: The power switch of each independent PR is controlled by the UPF, which is placed in the module itself. The EN control signal comes from the input port of the module.

- Isolation:

- The isolation of module-to-module signals are controlled by top-layer UPF, Which is placed in the dom_sys_top module of the SoC top, and fed power by Vdd_core_0v9

- The 3 modules of dom_isp, dom_vout, and dom_gpu contains 2-3 power domains. The isolation of the intra-module signals are controlled by the UPF of the module, which is placed on the top layer of the module and fed power by Vdd_core_0v9

- Level shifter:

- The dom_cpu output signal + high-to-low cell, place is dom_sys_top

- The dom_cpu input signal + low-to-high cell, place is dom_cpu_top

- For the signal overlap between Level l and ISO, select Level 1 cell with EN