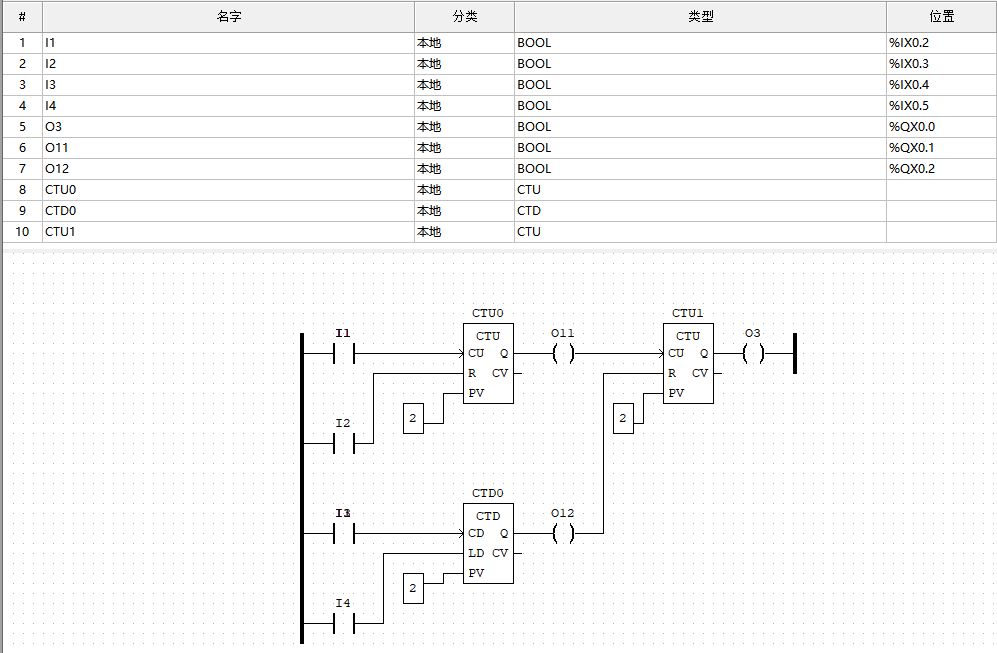

Counter Test

The counter blocks are verified in this section. Both up (CTU) and down (CTD) counters were used for this test. A CTU counter increments the internal count variable CV on every rising edge of the input CU. If the value in CV matches the user-defined PV variable, the output Q is set to true. In the event of a rising edge in the input R, the internal count variable CV is reset to zero. Similarly, the CTD counter loads the internal CV variable value from PV on the first rising edge of the input CD and decrements CV on every subsequent rising edge of the input CD. Once CV reaches zero, the output Q is set to true. Upon a rising edge on the input LD, the original PV value is restored to CV.

The output O3 is set to true if CTU1 evaluates to true at least two times before a reset pulse is received from CTD0. Inputs I1 and I2 are connected to the CU and R inputs of the CTU0 counter, while inputs I3 and I4 are connected to the CD and LD inputs of the CTD0 counter.