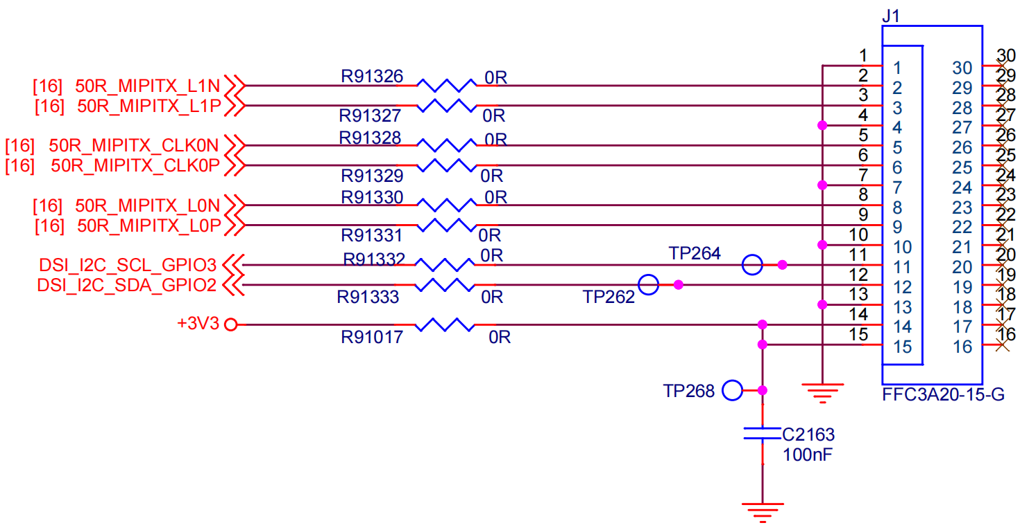

2-Lane MIPI DSI Pin Definition

The following figure and table describe the 2-lane MIPI DSI definition:

| No. | Definition | Description | Voltage |

|---|---|---|---|

| 1 | GND | Ground | - |

| 2 | 50R_MIPITX_L1N | MIPI Output Lane 1 Negative | 1.8 V |

| 3 | 50R_MIPITX_L1P | MIPI Output Lane 1 Positive | 1.8 V |

| 4 | GND | Ground | - |

| 5 | 50R_MIPITX_CLK0N | MIPI Output Clock 0 Negative | 1.8 V |

| 6 | 50R_MIPITX_CLK0P | MIPI Output Clock 0 Positive | 1.8 V |

| 7 | GND | Ground | - |

| 8 | 50R_MIPITX_L0N | MIPI Output Lane 0 Negative | 1.8 V |

| 9 | 50R_MIPITX_L0P | MIPI Output Lane 0 Positive | 1.8 V |

| 10 | GND | Ground | - |

| 11 | DSI_I2C_SCL_GPIO3 | DSI I2C SCL | 3.3 V |

| 12 | DSI_I2C_SDA_GPIO2 | DSI I2C SDA | 3.3 V |

| 13 | GND | Ground | - |

| 14 | +3.3 V | Power Voltage for digital circuit 3.3 V | 3.3 V |

| 15 | GND | GND | 1.8 V |