Clock and Reset

Block Diagram

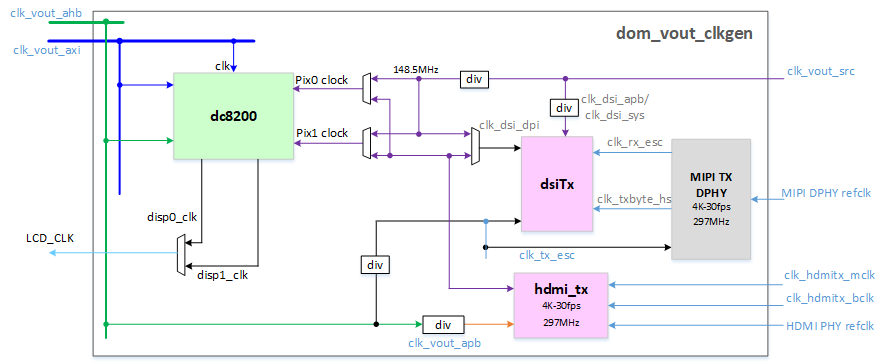

The display subsystem has these clock source, source clock for whole display subsystem, MIPI TX DPHY"s PLL reference clock, HDMI PHY"s reference clock, four channel I2S transmitter bit clock.

The clock division architecture is shown in the following diagram.

Specification

The clock and reset specification of the display subsystem is displayed in the

following table.

| Module | Clock | Internal | Default Freq (MHz) | Max Freq (MHz) | Typ. Freq (MHz) | Source0 | Source1 |

|---|---|---|---|---|---|---|---|

| clk_disp_root | TRUE | 0 | 1228.8 | 1228.8 | dom_vout_top.clk_vout_src | ||

| Source | clk_disp_axi | TRUE | 0 | 614.4 | 614.4 | dom_vout_top.clk_vout_axi | |

| clk_disp_ahb | TRUE | 0 | 204.8 | 204.8 | dom_vout_top.clk_vout_ahb | ||

| clk_hdmi_phy_ref | TRUE | 24 | 24 | 24 | dom_vout_top.clk_hdmiphy_ref | ||

| clk_hdmitx0_mclk | TRUE | 0 | 51.2 | 51.2 | dom_vout_top.clk_hdmitx0_mclk | ||

| clk_hdmitx0_sck | TRUE | 0 | 12.8 | 12.8 | dom_vout_top.clk_hdmitx0_bclk | ||

| clk_hdmitx0_pixelclk | TRUE | 0 | 297 | 0 | u0_hdmi_tx.clk_pix | ||

| clk_mipi_dphy_ref | TRUE | 12 | 12 | 12 | dom_vout_top.clk_mipiphy_ref | ||

| clk_mipitx_dphy_rxesc | TRUE | 0 | 10 | 0 | u0_mipitx_dphy.clk_rxesc | ||

| clk_mipitx_dphy_txbytehs | TRUE | 0 | 297 | 0 | u0_mipitx_dphy.clk_txbytehs | ||

| Divider | u0_pclk_mux.bist_pclk | FALSE | 50 | 50 | 50 | dom_vout_top.bist_pclk | |

| clk_disp_apb | TRUE | 0 | 51.2 | 51.2 | u0_pclk_mux.pclk | ||

| clk_apb | TRUE | 0 | 51.2 | 51.2 | clk_disp_ahb | ||

| u0_pclk_mux.func_pclk | FALSE | 0 | 51.2 | 51.2 | clk_apb | ||

| clk_dc8200_pix0 | TRUE | 0 | 307.2 | 307.2 | clk_disp_root | ||

| clk_dsi_sys | TRUE | 0 | 307.2 | 307.2 | clk_disp_root | ||

| clk_tx_esc | TRUE | 0 | 20.48 | 17.07 | clk_disp_ahb | ||

| Bus | u0_dom_vout_crg.pclk | TRUE | 0 | 51.2 | 51.2 | clk_disp_apb | |

| u0_dom_vout_syscon.pclk | FALSE | 0 | 51.2 | 51.2 | clk_disp_apb | ||

| u0_saif_amba_dom_vout_ahb_dec.clk_ahb | FALSE | 0 | 204.8 | 204.8 | clk_disp_ahb | ||

| u0_ahb2apb.clk_ahb | FALSE | 0 | 204.8 | 204.8 | clk_disp_ahb | ||

| u0_p2p_async.clk_apbs | FALSE | 0 | 51.2 | 51.2 | clk_disp_apb | ||

| u0_p2p_async.clk_apbm | FALSE | 0 | 307.2 | 307.2 | clk_dsi_sys | ||

| DC8200 | u0_dc8200.clk_axi | FALSE | 0 | 614.4 | 614.4 | clk_disp_axi | |

| u0_dc8200.clk_core | FALSE | 0 | 614.4 | 614.4 | clk_disp_axi | ||

| u0_dc8200.clk_ahb | FALSE | 0 | 204.8 | 204.8 | clk_disp_ahb | ||

| u0_dc8200.clk_pix0 | FALSE | 0 | 307.2 | 307.2 | clk_dc8200_pix0 | clk_hdmitx0_pixelclk | |

| u0_dc8200.clk_pix1 | FALSE | 0 | 307.2 | 307.2 | clk_dc8200_pix0 | clk_hdmitx0_pixelclk | |

| dom_vout_top.lcd_clk(gpio) | FALSE | 0 | 74.25 | 0 | u0_dc8200.clk_pix0_out | u0_dc8200.clk_pix1_out | |

| dsiTx | u0_cdns_dsiTx.clk_apb | FALSE | 0 | 307.2 | 307.2 | clk_dsi_sys | |

| u0_cdns_dsiTx.clk_sys | FALSE | 0 | 307.2 | 307.2 | clk_dsi_sys | ||

| u0_cdns_dsiTx.clk_dpi | FALSE | 0 | 307.2 | 307.2 | clk_dc8200_pix0 | clk_hdmitx0_pixelclk | |

| u0_cdns_dsiTx.clk_txesc | FALSE | 0 | 20.48 | 17.07 | clk_tx_esc | ||

| u0_cdns_dsiTx.clk_rxesc | FALSE | 0 | 10 | 0 | clk_mipitx_dphy_rxesc | ||

| u0_cdns_dsiTx.clk_txbytehs | FALSE | 0 | 297 | 0 | clk_mipitx_dphy_txbytehs | ||

| mipitx DPHY | u0_mipitx_dphy.clk_txesc | FALSE | 0 | 20.48 | 17.07 | clk_tx_esc | |

| u0_mipitx_dphy.clk_sys | FALSE | 0 | 51.2 | 51.2 | clk_disp_apb | ||

| u0_mipitx_dphy.clk_dphy_ref | FALSE | 12 | 12 | 12 | clk_mipi_dphy_ref | ||

| u0_mipitx_apbif.pclk | FALSE | 0 | 51.2 | 51.2 | clk_disp_apb | ||

| HDMI | u0_hdmi_tx.clk_mclk | FALSE | 0 | 51.2 | 51.2 | clk_hdmitx0_mclk | |

| u0_hdmi_tx.clk_bclk | FALSE | 0 | 12.8 | 12.8 | clk_hdmitx0_sck | ||

| u0_hdmi_tx.clk_sys | FALSE | 0 | 51.2 | 51.2 | clk_disp_apb | ||

| u0_hdmi_tx.clk_ref | FALSE | 24 | 24 | 24 | clk_hdmi_phy_ref | ||

For more information on the specification, see vout_clkrst_spec.xlsx.